计算机系统基础知识------计算机硬件

1. 计算机系统的基本概念

-

CPU的性能指标:主频、字长、CPU缓存、核心数量

-

总线的分类:数据总数、控制总线、地址总线

-

总线的性能指标:带宽、位宽、工作频率

-

BIOS(基本输入输出程序,保存ROM芯片中)/CMOS(RAM芯片,电池供电,保存BIOS数据,断电不丢失数据)

-

系统性能评测方法:时钟频率、指令执行(KIPS/MIPS)、等校指令速度法、数据处理速率(PDR)、核心程序法、基准测试程序。

-

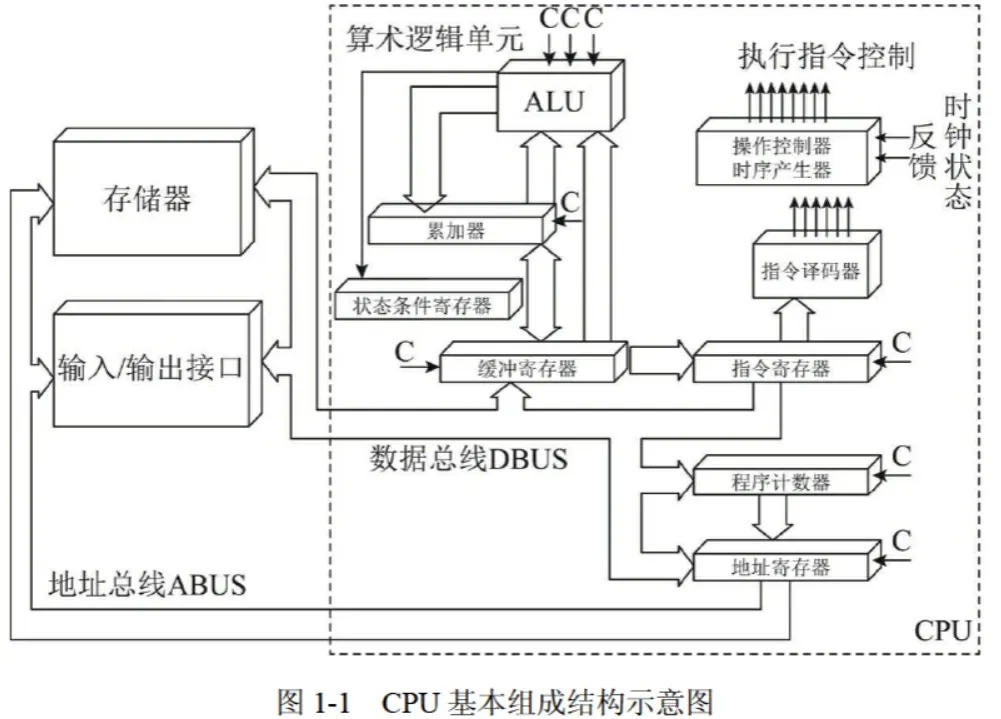

中央处理单元:

1. 功能:程序控制、操作控制、事件控制、数据处理

2. 组成:

运算器:算术逻辑单元ALU、累加寄存器(被减数暂存,运算数据结果暂存)、数据缓冲寄存器DR(暂存指令或数据字)、状态条件寄存器PSW(进位标志C、结果溢出标志V,0标志Z,负标志N,中断标志I,方向标志D,单步标志)等组成,负责数据加工处理,受控制器命令

控制器:正确执行,,异常处理,指令控制逻辑、时序控制逻辑、总线控制逻辑、中断控制逻辑 指令寄存器IR:暂存CPU指令 程序计数器PC:第一次是程序的第一条指令地址,之后是将要执行的下一条指令的地址 地址寄存器AR:当前CPU访问的内存单元地址 指令译码器ID:操作码和地址码

-

时序控制,为每条指令按时间顺序提供应有的控制信号,总线逻辑,为多个功能部件服务的信息通路的控制电路,中断控制逻辑,控制各种中断请求,根据优先级的高低对中断请求进行排队,诸葛交给CPU处理

-

多核CPU:一个单芯片上面集成两个甚至更多个处理器内核,每个内核有自己的逻辑单元、控制单元、中断处理器、运算单元、一级Cache,二级Cache共享或独有

-

存储器:

1. 所处位置的分类:内存、外存,

2. 按构成材料分类:磁存储器、半导体存储器、光存储器,

3. 工作方式分类:读写存储器、只读存储器(固定只读存储器ROM、可编程的只读存储器PROM、可擦除可编程的只读存储器EPROM、电可擦除可编程的只读存储器EEPROM、闪存Flash)

4. 按访问方式分类:按地址访问、按内容访问

5. 按寻址方式分类:随机存储器RAM,顺序存储器SAM,直接存储器DAM

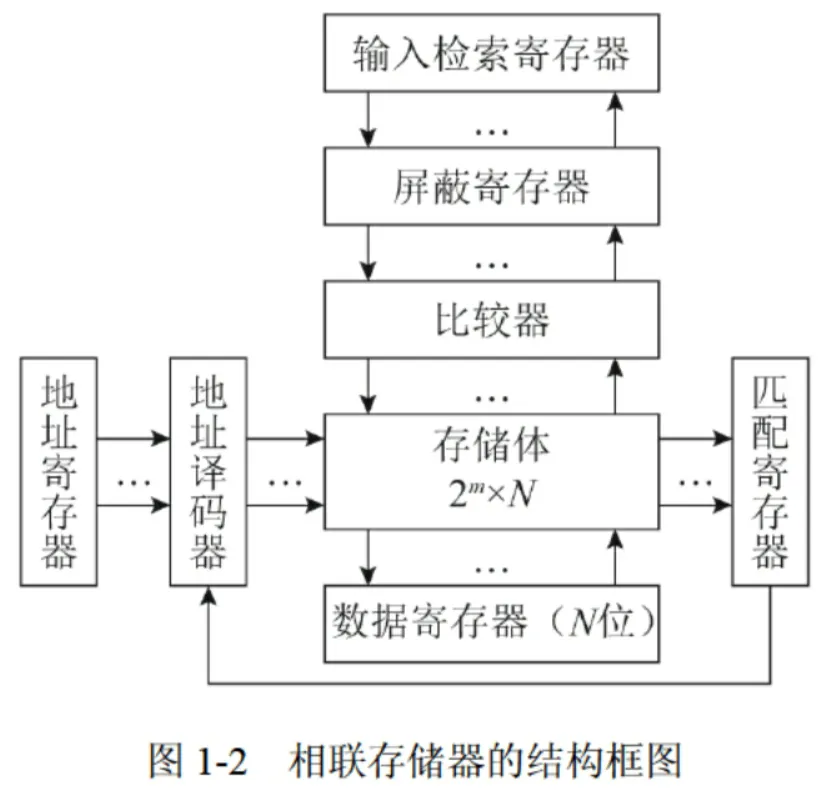

相联存储器:一种按内容访问的存储器,把数据或数据一部分作为关键字,按顺序写入信息,适合信息检索和更新

相联存储器中,输入检索寄存器用来存放要检索的内容(关键字),屏蔽寄存器用来屏蔽那些不参与检索的字段,比较器将检索的关键字与存储体的每一单元进行比较。每一位有一个比较器

常用来作为段表、页表、块表,用在数据库和知识库中

-

高速缓存:存放当前最活跃的按程序和数据

1. 组成:Cache 存储器中控制部分的功能是判断 CPU 要访问的信息是否在 Cache 存储器中,若在即为命中,若不在则没有命中。命中时直接对 Cache 存储器寻址;未命中时,要按照替换原则决定主存的一块信息放到 Cache 存储器的哪一块里。

2. 地址映像方法:直接映像(主存的块与Cache对应的块是固定的,灵活性差,地址变换简单)、全相联映像(主存的任意一块可以调入Cache,分块,块内地址大小为相联存储器大小,利用主存地址高位表示的主存块号与Cache中相联存储器单元所有单元中记录的主存块号进行比较,无法从主存块号中直接获得Cache块号,变换比较复杂,速度慢,调入Cache位置灵活)

3. 组相联映像:将Cache中的块分成组,主存任何区的0组只能存到Cache的0组中,1组只能存到Cache的1组中

-

替换算法:随即替换算法、先进先出算法、近期最少使用算法、优化替换算法

什么是Cache

-

功能:提高CPU数据输入输出的速率,突破所谓的“冯*诺依曼瓶颈”。

-

速度:在计算机的存储系统体系中,Cache是访问速度较快的层次。

-

原理:使用Cache改善系统性能的依据是程序的局部性原理。

-

组成:Cache由两部分组成:控制部分和Cache存储器部分。

平均系统周期时间(以读操作为例:使用“Cache + 主存储器”)

多级Cache原理

Cache和主存之间的交互功能全部由硬件来实现,主存和辅存的交互功能由硬件和软件结合起来实现。

多级Cache技术是指利用一个大的二级Cache来处理一级Cache的缺失,一级Cache是CPU的第一层高速缓存,分为数据缓存和指令缓存,内置于CPU中,均由静态RAM组成(无需动态刷新,但集成度低,占用面积比动态RAM大 6倍),受CPU工艺影响无法做得太大,L1级的Cache一般容量在32~256KB之间。

L2级别的Cache是CPU的第二层高速缓存,由高速动态RAM组成,分为片内和片外两种芯片,内存的芯片二级缓存运行速度与主频相同,而外部二级缓存则只有主频的一半。目前家用CPU L2 Cache的最大容量是4MB。

地址映像

在计算机运行的过程中,需要知道Cache与内存地址的影射关系,需要由一块存储器保存相关映射数据,成为地址映像。

-

通常是由SRAM(Static Random Access Memory静态存储器)组成,其访问速度远高于主存,接近CPU。

-

其功能是提高CPU数据输入输出的速率。其理论依据是程序的局部性原理,实现基础是将主存和Cache划分为大小相同的块/页。

-

装入缓存时将主存块与Cache块的映射关系存入相联存储表(硬件实现)中。

-

CPU通过主存地址访存时先访问Cache(命中可提高速度,所以其关键性性能指标是命中率),依据==主存地址关联相联存储表==转换为Cache地址。如果在Cache中没有,才需要访问主存(Cache页置换,置换算法也会影响命中率)。

地址映像方式

-

直接映像和变换

-

主存储器中一块只能映射到Cache的一个特定块中

-

主存与缓存分成相同大小的数据块

-

主存空间按缓存容量分成区,每一区的块数与缓存的总块数相等。

-

主存中某区的一块存入缓存时只能存入缓存中块号相同的位置。

特点:

-

地址变换电路简单,访问速度快

-

空间利用率低,冲突概率高

-

对页面置换算法以来度较高,且Cache空间利用率较低,命中率较低。

-

全相联地址映像和变换

-

主存的任意一块可以映射到cache中的任意一块的位置上

-

主存与缓存分成相同大小的数据块

-

主存的某一数据块可以装入缓存的任意一块空间中

特点:

-

空间利用率高,命中率较高

-

冲突概率低

-

实现复杂,速度慢,适合小容量cache

-

组相联地址映像和变换

-

主存和cache按相同大小分块

-

cache分为若干组,如两块一组,主存按cache组数分区

-

每个组采用直接映射方式

-

组内的块则采用全相联映像方式

特点:

-

是以上两种方式的折衷

-

实现难度和造价要比直接映像方式高

Cache性能:命中率、Cache存取时间,主存访问事件

-

虚拟存储器:扩大主存容量

-

外存储器:磁盘(磁道track、扇区sector、柱面cylinder,寻址信息包括磁盘驱动号、柱面号、磁头号、数据块号、交换量,读写时间取决于传送时间、寻道时间、旋转时间、)、光盘存储器、固态硬盘SSD(控制芯片、缓存芯片、闪存芯片)

计算非格式化容量

容量 = 面数 x (磁道数/面)x 内圆周长 x 最大位密度

计算格式化容量

容量 = 面数 x (磁道数/面)x (扇区数/道)x(字节数/扇区)

-

磁盘阵列技术RAID(redundant array of Independent disk):多台磁盘存储器组成的一个快速,大容量,高可靠的外存子系统

-

存储域网络SAN(stronge area network):存储器和服务器连接的网络,将不同地点的RAID组成一个逻辑存储设备

总线

-

按传输类型,分为数据总线、地址总线、控制总线 控制芯片组,集成在主板上

北桥芯片直接与 CPU、内存、显卡、南桥相连,控制着 CPU 的类型、主板的总线频率、内存控制器、显示核心等。前端总线(FSB)是将 CPU 连接到北桥芯片的总线。内存总线是将内存连接到北桥芯片的总线。用于和北桥之间的通信,显卡则通过 IO 总线

连接到北桥芯片。南桥芯片主要负责外部设备接口与内部 CPU的联系,其中,通过 O 总线连接外部IO 设备连接到南桥,例如 USB 设备、ATA 和 SATA 设备以及一些扩展接口,扩展总线则指是主板上提供的一些 PCI、ISA 等插槽。

单芯片结构没有北桥

常见总线ISA总线、EISA总线、PCI总线、PCIE总线、前端总线、RS232C、SCSI总线(并行)、SATA(Serial ATA)、USB、IEEE-1394、IEEE-488

总线的性能指标:

带宽(bit/s,单位时间内能处理的数据量) = 位宽(bit,总线宽度)x 工作频率(Hz, 1/s)

输入输出控制

-

IO有单独的内存空间

-

访问方式:无条件传送、程序查询

-

中断方式:多中断信号线、中断软件查询、菊花链、总线仲裁、中断向量表

-

DMA方式,直接内存存取,以块为单位,所以说dma将一块数据传输到内存中,DMA传输可以分为中央处理器停止法、总线周期分时法、总线周期挪用法,在传送数据块的过程中不需要CPU干涉(过程开启和结束时需要CPU处理,传送数据过程中不需要CPU干预。)

-

DMA的工作方式:

-

向CPU申请DMA传送

-

CPU允许后,DMA接受系统总线的控制权

-

在DMA控制器的控制下,在主存和外部存储器之间交换数据,交换过程中不需要CPU的参与,传送开始前需要CPU提供传送数据的起始地址和数据长度。

-

传送结束后,向CPU返回操作完成信号。

输入输出处理机(IOP):通道是一个特殊功能的处理器,外围处理机是专用处理机

评论