网络工程师-核心考点:计算机硬件基础全解析

一、引言

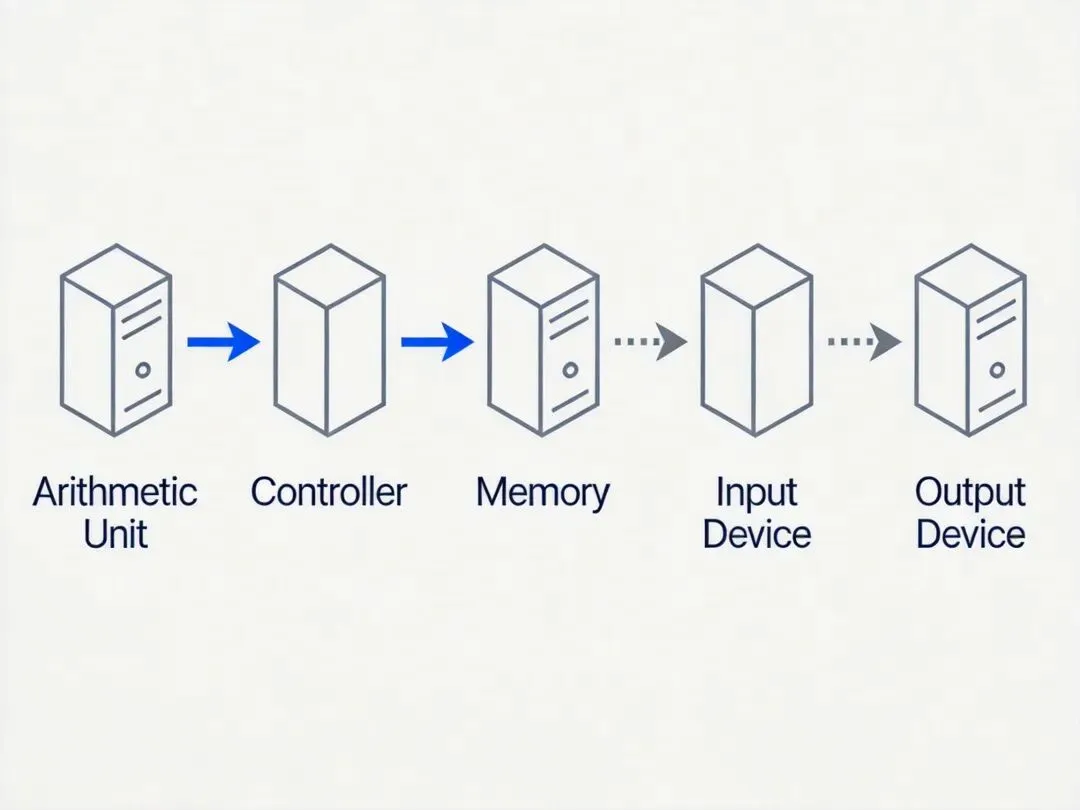

二、冯・诺依曼体系结构

2.1 五大核心部件功能详解

2.2 考点记忆与易混点辨析

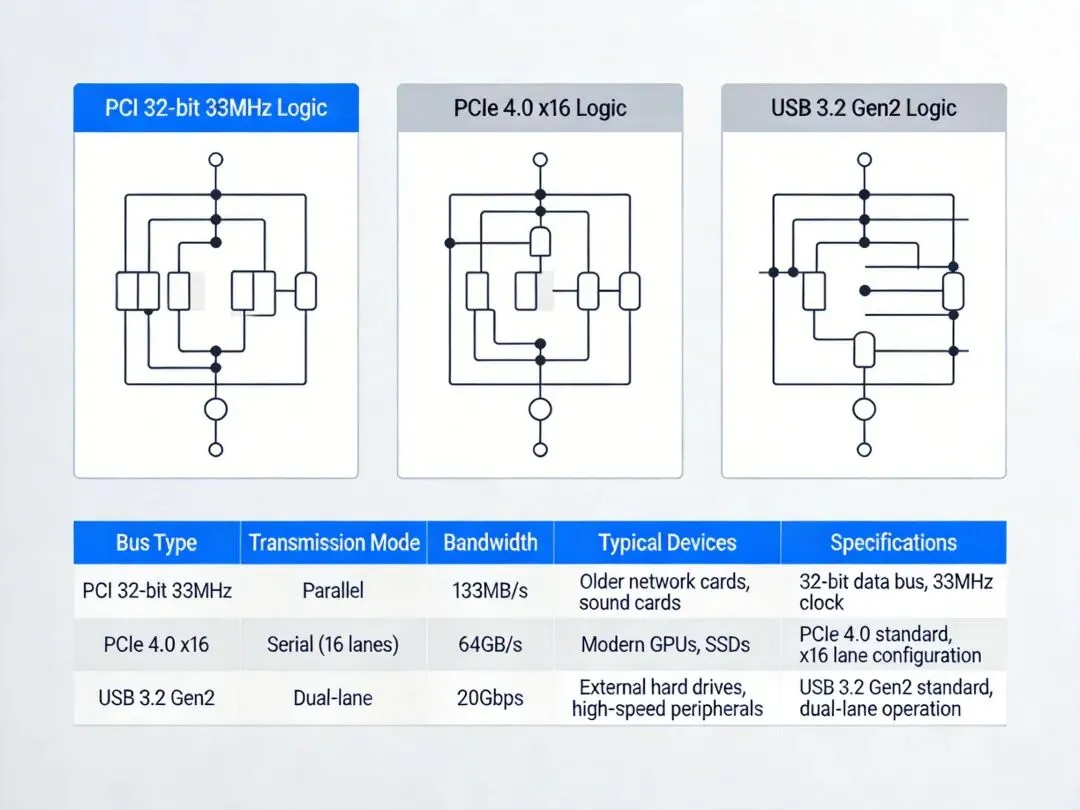

三、计算机总线技术

3.1 按传输信息分类

3.2 按数据传输方式分类

3.3 方案对比与行业标准

|

|

|

|

|

|

|---|---|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

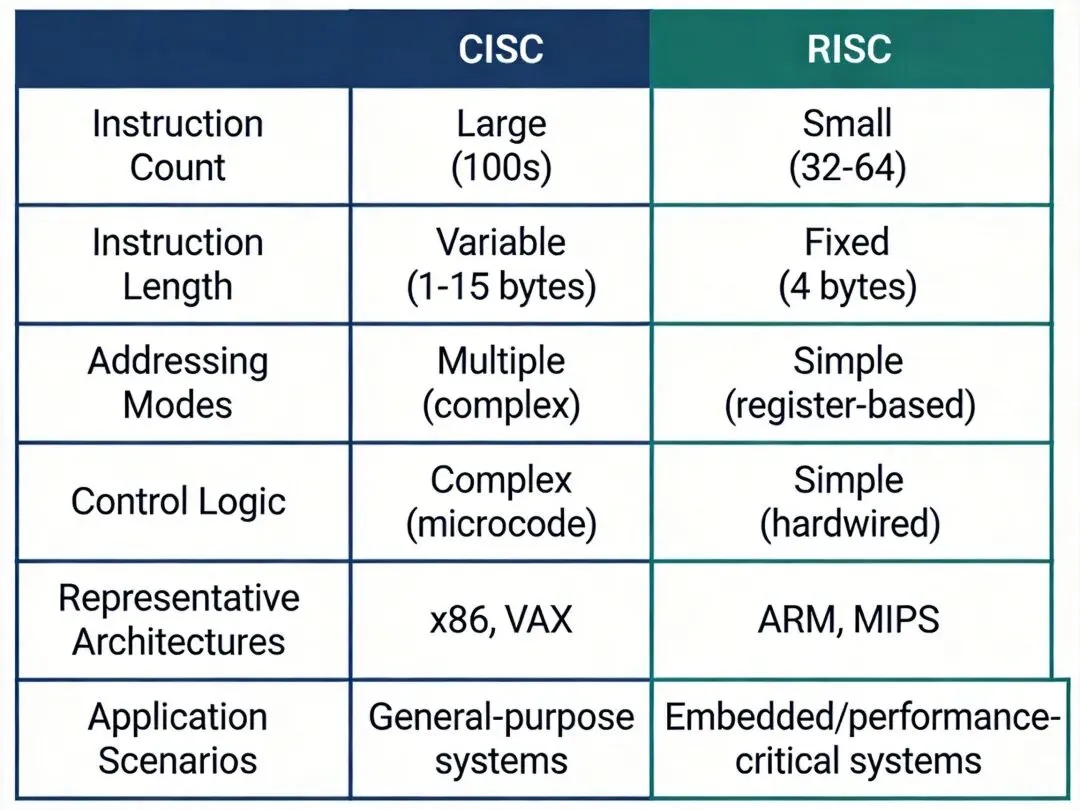

四、寻址方式与指令集架构

4.1 常见寻址方式

4.2 CISC 与 RISC 指令集对比

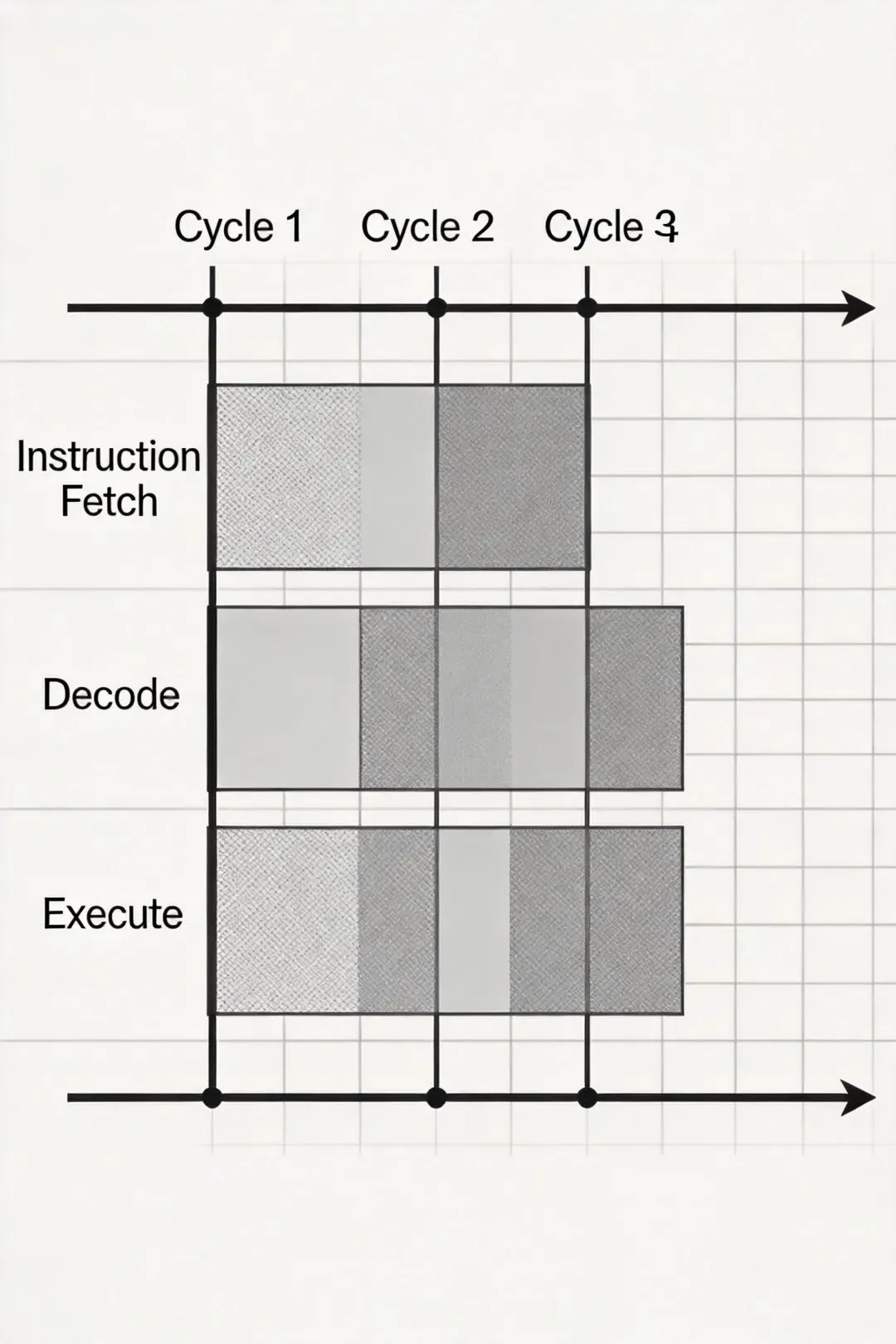

五、流水线技术(计算核心考点)

5.1 核心原理与参数定义

5.2 性能指标计算

5.3 典型真题解析

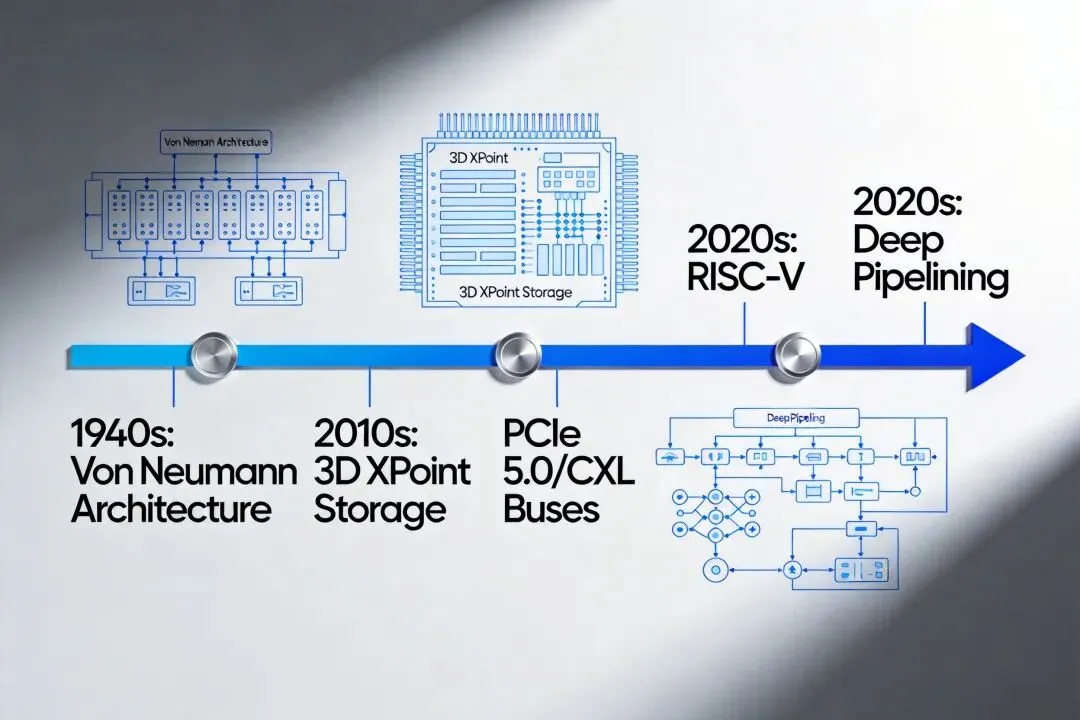

六、技术发展与考试趋势

6.1 技术演进方向

6.2 考试命题趋势

七、总结与备考建议

7.1 核心考点提炼

7.2 备考与应试建议

THE END -

点击下方卡片关注我 点个小赞你必上岸↓↓↓

评论